基本概念

在 Verilog 中,$random 是一种用于生成伪随机数的系统任务。它可以根据种子变量 (seed) 的值返回一个 32 位有符号整型随机数。如果没有提供种子变量,默认会使用内部定义的种子值。其调用格式有3种:$random;$random();$random(seed);

$random与$random()

其中$random;和$random();的效果是相同的。

$random的返回值是一个32位的整数,但是有时不见得需要这么大的数。如果希望随机数的值能固定在某个范围,那么可以这么使用:$random%b;那么生成的随机数的范围就是 [ ( -b+1 ) : (b- 1 ) ]。

initial beginrand_data = 0;repeat(5) begin#10 rand_data = $random; //每10ns产生一个随机数,重复五次end#5;$stop;

end![]()

$random改成$random%10。即,正数范围的随机数生成结果[0:9]

![]()

如果想随机产生的是正整数,则使用{$random} % b;表示 0:(b-1)中的随机数

$random(seed)

种子的作用

种子变量决定了每次调用 $random 所产生的随机数值。如果希望获得可重复的结果以便调试或验证,可以通过设置固定的种子实现这一点;反之,若需要不可预测的序列,则应频繁更改种子或者不显式设定种子让其自动生成新值。

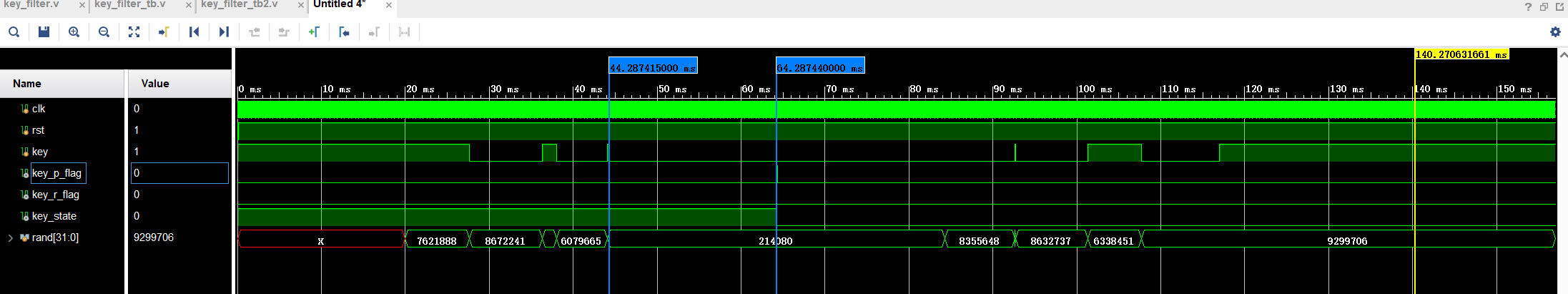

`timescale 1ns / 1psmodule key_filter_tb2();reg clk,rst;reg key;wire key_p_flag;wire key_r_flag;wire key_state; key_filter key_filter(clk,rst,key,key_p_flag,key_r_flag,key_state);initial clk=1;always #10 clk=~clk;initial beginrst=0;key=1;#201;rst=1;#3000;press_key(2);$stop;endreg[31:0]rand;task press_key;input [3:0]seed;beginkey=1;#20000000;repeat(5)beginrand={$random(seed)} % 10000000; #rand key=~key; endkey=0;#40000000;repeat(5)beginrand={$random(seed)} % 10000000; #rand key=~key; endkey=1;#40000000; end endtask endmodule随机产生时间来测试按键消抖。

结果与预期相符。