灯

约束文件

set_property PACKAGE_PIN W5 [get_ports CLK]

set_property PACKAGE_PIN U18 [get_ports rst]

set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property PACKAGE_PIN U19 [get_ports {led[2]}]

set_property PACKAGE_PIN V19 [get_ports {led[3]}]

set_property PACKAGE_PIN W18 [get_ports {led[4]}]

set_property PACKAGE_PIN U15 [get_ports {led[5]}]

set_property PACKAGE_PIN U14 [get_ports {led[6]}]

set_property PACKAGE_PIN V14 [get_ports {led[7]}]

set_property PACKAGE_PIN V13 [get_ports {led[8]}]

set_property PACKAGE_PIN V3 [get_ports {led[9]}]

set_property PACKAGE_PIN W3 [get_ports {led[10]}]

set_property PACKAGE_PIN U3 [get_ports {led[11]}]

set_property PACKAGE_PIN P3 [get_ports {led[12]}]

set_property PACKAGE_PIN N3 [get_ports {led[13]}]

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property PACKAGE_PIN L1 [get_ports {led[15]}]

set_property PACKAGE_PIN V16 [get_ports {sel[1]}]

set_property PACKAGE_PIN V17 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property IOSTANDARD LVCMOS33 [get_ports rst]CLK、rst、sel都是自定义的端口名,可做相应修改

数码管

约束文件

set_property PACKAGE_PIN W5 [get_ports CLK]

set_property PACKAGE_PIN V17 [get_ports SW_in]

set_property IOSTANDARD LVCMOS33 [get_ports SW_in]

set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN W4 [get_ports {display_out[10]}]

set_property PACKAGE_PIN V4 [get_ports {display_out[9]}]

set_property PACKAGE_PIN U4 [get_ports {display_out[8]}]

set_property PACKAGE_PIN U2 [get_ports {display_out[7]}]

set_property PACKAGE_PIN W7 [get_ports {display_out[6]}]

set_property PACKAGE_PIN W6 [get_ports {display_out[5]}]

set_property PACKAGE_PIN U8 [get_ports {display_out[4]}]

set_property PACKAGE_PIN V8 [get_ports {display_out[3]}]

set_property PACKAGE_PIN U5 [get_ports {display_out[2]}]

set_property PACKAGE_PIN V5 [get_ports {display_out[1]}]

set_property PACKAGE_PIN U7 [get_ports {display_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[10]}]像CLK、SW_in、display_out这些,可通过自己定义的端口进行相应的修改

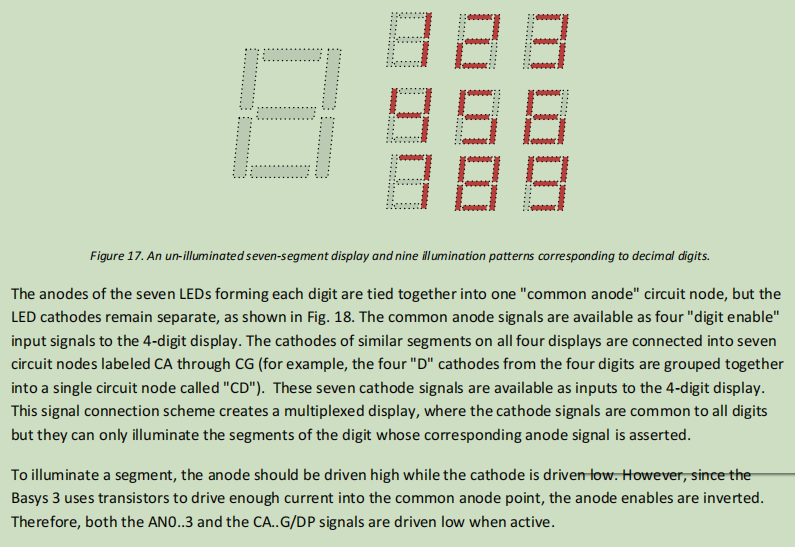

数码管是共阳极的,阳极通过晶体管驱动,所以当需要点亮某个段时,阳极应该被拉低(因为晶体管是反向驱动的)。另外,显示控制器需要以一定的刷新率循环点亮四个数码管,每个数码管依次显示一段时间,利用人眼的视觉暂留效应让四个数码管看起来同时亮起。刷新率一般在1kHz到60Hz之间,每个数码管的点亮时间大约是刷新周期的四分之一,比如16ms的周期,每个数码管点亮4ms。

Basys 3板上的七段数码管是共阳极的,每个数码管的七个段(加上小数点)的阴极是分开的,而阳极是共用的。每个段的LED通过330欧姆的电阻连接到FPGA的I/O引脚,当对应的引脚输出高电平时,LED会点亮。但是根据前面的描述,由于驱动电路中的反向晶体管,实际有效的信号可能是低电平激活。

如何通过分时复用来控制四个数码管。例如,当AN0(第一个数码管的阳极)有效时,设置相应的阴极信号来显示特定的数字,然后依次切换到AN1、AN2、AN3,每个阳极的有效时间相同,循环往复。

总结

数码管为共阳极结构,阳极通过反向晶体管驱动,因此阳极有效信号为低电平。

显示控制采用分时复用技术,每个数码管依次点亮,刷新率需高于人眼感知阈值(如1kHz到60Hz)。

每个数码管点亮时间为刷新周期的四分之一(如16ms总周期,每个数码管点亮4ms)。

Basys 3板的七段数码管为四位数码管,共阳极设计,阴极分段控制。

段选信号(阴极)需设置为低电平以点亮对应段,阳极通过FPGA引脚输出低电平激活(因驱动电路反向)。

具体时序示例说明:通过循环切换阳极(AN0-AN3)并同步设置阴极信号,实现多位数显示。

刷新周期建议为1ms-16ms,每个数码管点亮时间为刷新周期的四分之一(如4ms)。

dispaly.v

显示1234和4321

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2015/12/02 22:02:29

// Design Name:

// Module Name: display

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module display(input CLK,input SW_in,output reg[10:0] display_out);reg [19:0]count=0;reg [2:0] sel=0;parameter T1MS=50000;always@(posedge CLK)beginif(SW_in==0)begincase(sel)0:display_out<=11'b0111_1001111;1:display_out<=11'b1011_0010010;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1001100;default:display_out<=11'b1111_1111111;endcaseendelsebegincase(sel)0:display_out<=11'b1110_1001111;1:display_out<=11'b1101_0010010;2:display_out<=11'b1011_0000110;3:display_out<=11'b0111_1001100;default:display_out<=11'b1111_1111111;endcaseendendalways@(posedge CLK)begincount<=count+1;if(count==T1MS)begincount<=0;sel<=sel+1;if(sel==4)sel<=0;endend

endmodule模块有三个端口:CLK(时钟输入),SW_in(开关输入),display_out(11位的输出寄存器)。display_out可能对应四个数码管的阳极选择(4位)和七段的阴极控制(7位),总共11位。例如,假设前4位是四个数码管的阳极使能,后7位是阴极控制(CA到CG)。

在第一个always块中,当SW_in为0时,根据sel的值(0到3),设置不同的display_out。例如,当sel=0时,display_out是11'b0111_1001111。这里前四位是0111,可能表示选择第一个数码管(因为AN0是低电平有效,而0111中的第一位是0),后面七位是1001111,对应七段显示的数字。类似地,其他sel值对应不同的数码管和显示内容。当SW_in为1时,display_out的阳极选择位相反,可能是数码管的顺序被反转。

第二个always块用于生成sel信号,即选择当前要点亮的数码管。计数器count在每次时钟上升沿递增,当达到T1MS(50000)时,sel加1,循环在0到3之间。这样,每个数码管的显示时间由count的溢出频率决定。例如,如果时钟频率是50MHz,那么每个计数周期是20ns,T1MS=50000对应1ms的计数溢出。因此,每个数码管的点亮时间是1ms,四个数码管的总刷新周期是4ms,对应250Hz的刷新率,这在人眼可接受的范围内,不会有明显的闪烁。

模块功能

通过分时复用控制四位数码管,循环点亮每一位并显示特定内容,具体逻辑如下:

信号定义:

display_out[10:0]:11位输出信号,前4位控制阳极(AN0-AN3),后7位控制阴极(CA-CG)。

sel[2:0]:数码管选择信号(0-3),用于切换当前点亮的数码管。

count:计数器,用于控制刷新频率。

T1MS=50000:假设时钟为50MHz时,计数至50000对应1ms(20ns * 50000 = 1ms)。显示逻辑(第一个always块):

SW_in=0时:

sel=0:选中第一个数码管(display_out=0111_1001111),即AN0低电平,阴极显示“1”(对应1001111)。

sel=1:选中第二个数码管(display_out=1011_0010010),即AN1低电平,阴极显示“2”(对应0010010)。类似逻辑依次控制第3、4位数码管。

SW_in=1时:

阳极选择顺序反转,例如

sel=0对应AN3(display_out=1110_1001111),实现数码管点亮顺序的逆向切换。刷新逻辑(第二个always块):

计数器

count累加,每1ms(达到T1MS)切换一次sel,循环范围为0-3。每个数码管点亮时间为1ms,总刷新周期为4ms(对应250Hz刷新率),满足无闪烁要求。

关键设计细节

阳极控制:前4位为

AN3-AN0(高位在前),例如0111表示AN0有效(低电平),其余无效(高电平)。阴极编码:后7位为七段码(CA-CG),例如

1001111对应段码“1”(CA=1, CB=0, CC=0, CD=1, CE=1, CF=1, CG=1)。刷新机制:通过快速循环切换阳极和同步更新阴极,利用视觉暂留效应实现四位数码管“同时”显示。

流水灯

`timescale 1ns / 1ps

module led_display(input CLK, // 系统时钟(假设50MHz)input RST, // 复位信号output reg [15:0] LED, // 16位流水灯输出output reg [3:0] AN, // 数码管位选(AN0-AN3,低电平有效)output reg [6:0] SEG // 七段码输出(CA-CG,低电平有效)

);// 分时复用控制参数

reg [19:0] cnt_refresh = 0; // 刷新计数器(1ms刷新周期)

reg [1:0] sel = 0; // 数码管选择信号

reg [15:0] shift_reg = 16'h0001; // 流水灯移位寄存器(初始值1)// 七段译码表(0-F,共阴极编码,需根据实际硬件调整)

function [6:0] seg_decoder;input [3:0] data;begincase(data)4'h0: seg_decoder = 7'b0000001; // 04'h1: seg_decoder = 7'b1001111; // 14'h2: seg_decoder = 7'b0010010; // 24'h3: seg_decoder = 7'b0000110; // 34'h4: seg_decoder = 7'b1001100; // 44'h5: seg_decoder = 7'b0100100; // 54'h6: seg_decoder = 7'b0100000; // 64'h7: seg_decoder = 7'b0001111; // 74'h8: seg_decoder = 7'b0000000; // 84'h9: seg_decoder = 7'b0000100; // 9default: seg_decoder = 7'b1111111; // 灭endcaseend

endfunction// 流水灯移位逻辑(每秒移位一次)

reg [25:0] cnt_shift = 0;

always @(posedge CLK) beginif (RST) beginshift_reg <= 16'h0001; // 复位时初始化为1end else begincnt_shift <= cnt_shift + 1;if (cnt_shift == 50_000_000) begin // 1秒移位一次(50MHz时钟)shift_reg <= {shift_reg[14:0], shift_reg[15]}; // 循环左移cnt_shift <= 0;endendLED <= shift_reg; // 输出流水灯状态

end// 数码管动态扫描逻辑

always @(posedge CLK) begincnt_refresh <= cnt_refresh + 1;if (cnt_refresh == 50_000) begin // 1ms刷新周期(50MHz时钟)cnt_refresh <= 0;sel <= sel + 1; // 切换数码管end

end// 数码管数据选择与七段译码

always @(*) begincase(sel)2'b00: beginAN = 4'b1110; // 选中第1位数码管(AN0低电平)SEG = seg_decoder(shift_reg[3:0]); // 显示低4位流水灯状态end2'b01: beginAN = 4'b1101; // 选中第2位数码管(AN1低电平)SEG = seg_decoder(shift_reg[7:4]); // 显示次低4位end2'b10: beginAN = 4'b1011; // 选中第3位数码管(AN2低电平)SEG = seg_decoder(shift_reg[11:8]); // 显示次高4位end2'b11: beginAN = 4'b0111; // 选中第4位数码管(AN3低电平)SEG = seg_decoder(shift_reg[15:12]); // 显示高4位enddefault: beginAN = 4'b1111; // 默认关闭所有数码管SEG = 7'b1111111;endendcase

endendmodule选中某一个数码管

module SoC(input wire clk0, input wire rst,/*IO interface*/input wire [1:0] sel,output reg[10:0] displayout,//output wire[15:0] led

);

wire[6:0] out1;

wire[6:0] out2;

wire[6:0] out3;

wire[6:0] out4;

shumaguan U1(out1,led[3:0]);

shumaguan U2(out2,led[7:4]);

shumaguan U3(out3,led[11:8]);

shumaguan U4(out4,led[15:12]);

always@(*)beginif(led[3:0]>0) displayout={4'b1110,out1};else if(led[7:4]>0) displayout={4'b1101,out2};else if(led[11:8]>0) displayout={4'b1011,out3};else if(led[15:12]>0) displayout={4'b0111,out4};endwire clk;clk_div clk_div0(.clk(clk0),.rst(rst),.Clk_CPU(clk));//........xdc

set_property PACKAGE_PIN W5 [get_ports clk0]

set_property PACKAGE_PIN W16 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports clk0]

set_property PACKAGE_PIN W4 [get_ports {displayout[10]}]

set_property PACKAGE_PIN V4 [get_ports {displayout[9]}]

set_property PACKAGE_PIN U4 [get_ports {displayout[8]}]

set_property PACKAGE_PIN U2 [get_ports {displayout[7]}]

set_property PACKAGE_PIN W7 [get_ports {displayout[6]}]

set_property PACKAGE_PIN W6 [get_ports {displayout[5]}]

set_property PACKAGE_PIN U8 [get_ports {displayout[4]}]

set_property PACKAGE_PIN V8 [get_ports {displayout[3]}]

set_property PACKAGE_PIN U5 [get_ports {displayout[2]}]

set_property PACKAGE_PIN V5 [get_ports {displayout[1]}]

set_property PACKAGE_PIN U7 [get_ports {displayout[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[10]}]set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property PACKAGE_PIN U19 [get_ports {led[2]}]

set_property PACKAGE_PIN V19 [get_ports {led[3]}]

set_property PACKAGE_PIN W18 [get_ports {led[4]}]

set_property PACKAGE_PIN U15 [get_ports {led[5]}]

set_property PACKAGE_PIN U14 [get_ports {led[6]}]

set_property PACKAGE_PIN V14 [get_ports {led[7]}]

set_property PACKAGE_PIN V13 [get_ports {led[8]}]

set_property PACKAGE_PIN V3 [get_ports {led[9]}]

set_property PACKAGE_PIN W3 [get_ports {led[10]}]

set_property PACKAGE_PIN U3 [get_ports {led[11]}]

set_property PACKAGE_PIN P3 [get_ports {led[12]}]

set_property PACKAGE_PIN N3 [get_ports {led[13]}]

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property PACKAGE_PIN L1 [get_ports {led[15]}]

set_property PACKAGE_PIN V16 [get_ports {sel[1]}]

set_property PACKAGE_PIN V17 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

shumaguan.v

module shumaguan(out,in);input[3:0] in;output reg[6:0] out;

always@(*)case(in)4'h0:out=7'b0000001;4'h1:out=7'b1001111;4'h2:out=7'b0010010;4'h3:out=7'b0000110;4'h4:out=7'b1001100;4'h5:out=7'b0100100;4'h6:out=7'b0100000;4'h7:out=7'b0001111;4'h8:out=7'b0000000;4'h9:out=7'b0000100;4'ha:out=7'b0001000;4'hb:out=7'b1100000;4'hc:out=7'b0110001;4'hd:out=7'b1000010;4'he:out=7'b0110000;4'hf:out=7'b0111000;default: out=7'b0000001;endcase

endmodule

分时复用

module SoC(input wire clk0, input wire rst,/*IO interface*/input wire [1:0] sel,output reg [10:0] displayout, // 前4位控制AN,后7位控制段码output wire [15:0] led

);wire [6:0] out1, out2, out3, out4;reg [19:0] cnt_refresh = 0; // 刷新计数器(假设50MHz时钟)reg [1:0] sel_scan = 0; // 数码管动态扫描选择信号// 七段译码模块实例化shumaguan U1(out1, led[3:0]);shumaguan U2(out2, led[7:4]);shumaguan U3(out3, led[11:8]);shumaguan U4(out4, led[15:12]);// 分时复用控制逻辑always @(posedge clk0) beginif (rst) begincnt_refresh <= 0;sel_scan <= 0;end else begincnt_refresh <= cnt_refresh + 1;if (cnt_refresh == 50_000) begin // 1ms刷新周期(50MHz时钟)cnt_refresh <= 0;sel_scan <= sel_scan + 1;endendend// 数码管动态扫描输出always @(*) begincase (sel_scan)2'b00: displayout = {4'b1110, out1}; // 选中第1位数码管(AN0低电平)2'b01: displayout = {4'b1101, out2}; // 选中第2位数码管(AN1低电平)2'b10: displayout = {4'b1011, out3}; // 选中第3位数码管(AN2低电平)2'b11: displayout = {4'b0111, out4}; // 选中第4位数码管(AN3低电平)default: displayout = 11'b1111_1111111; // 默认关闭endcaseend// 其余原有代码保持不变(时钟分频、MIPS、内存等)wire clk;clk_div clk_div0(.clk(clk0),.rst(rst),.Clk_CPU(clk));// ...(其他模块实例化代码)

endmodule