电路板和器件规划简介

正确规划电路板上器件的定向并将信号分配给特定的引脚,这样可以显著改进系统整体性能、功耗和设计周期。可视

化器件与印刷电路板 (PCB) 之间的物理和逻辑互动方式,使您可以优化通过器件的数据流。

未正确规划 I/O 配置则可能导致系统性能下降和设计收敛时间延长。赛灵思强烈建议在考虑 I/O 管脚分配的同时进行电

路板级规划。

如需了解更多信息,请参阅以下资料:

•

《 Vivado Design Suite 用户指南: I/O 管脚分配和时钟规划》 (UG899) [ 参照 7]

• Vivado Design Suite QuickTake 视频教程: I/O 管脚分配简介

PCB 布局建议

电路板上器件的布局与其它组件的互动会对 I/O 管脚分配产生巨大影响。

与 PCB 上的物理组件保持一致

首先应确定器件在 PCB 上的定向。还要考虑固定 PCB 组件的位置,以及内部器件资源。例如,器件封装的千兆位收发

器接口尽量靠近在 PCB 上与其连接的组件,这样可以缩短 PCB 走线长度,同时减少 PCB 过孔数量。

制作一张包含关键接口的 PCB 草图,通常有助于确定 FPGA 器件在 PCB 上的最佳定向,以及 PCB 组件的布局。完成以

后继续规划其余的 FPGA I/O 接口。

像存储器这样的高速接口可以通过非常短的走线直接与 PCB 组件连接。如有可能,这些 PCB 走线经常需要长度匹配,

并且不能使用 PCB 过孔。在这种情况下,偏向于选择最接近器件边缘的封装引脚,以保持较短的连接,同时避免布线

超出 BGA 引脚的大矩阵。

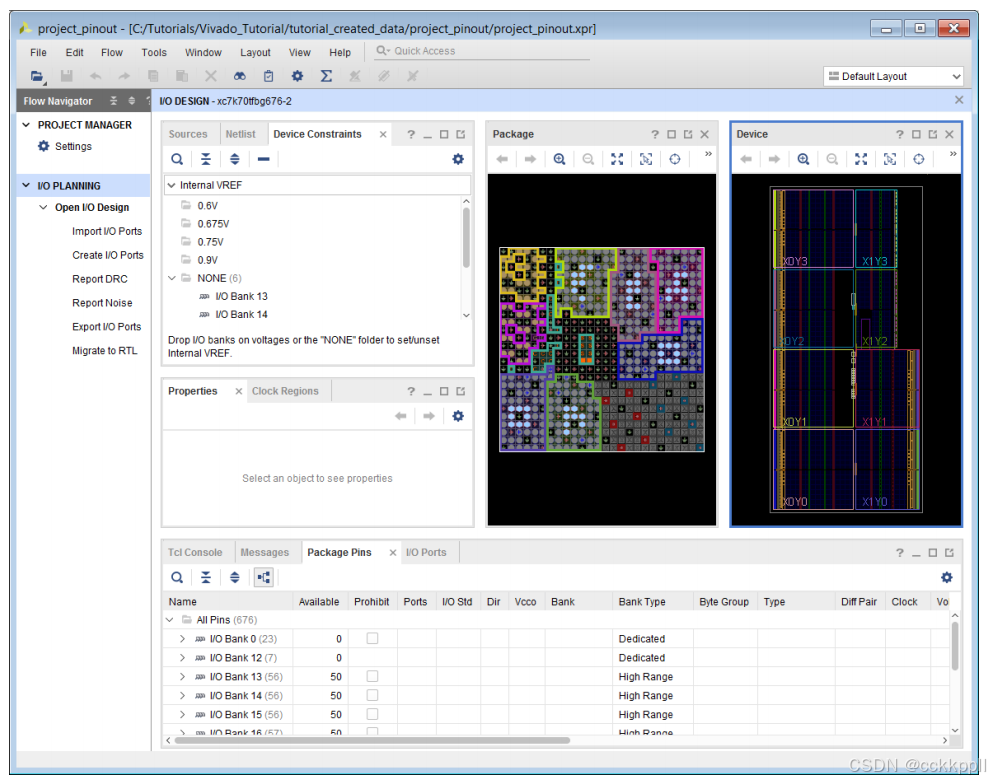

在该阶段, Vivado IDE 中的 “I/O Planning” 布局有助于对物理器件尺寸相关的 I/O 连接进行可视化,能够展示顶视图与

底视图。

重要提示: 对于热管理存在难度的设计,布局时应注意与其他高功耗组件的对应间隙,以最大限度减少热耦合并增加

空气流动。避免将器件置于另一个高功耗组件的散热气流内,或是任何电路板上热量能对器件工作温度产生不利影响

的位置。赛灵思建议开展热仿真,了解布局与环境条件如何影响器件的结温。

下列数据展示了 “I/O Planning” 布局。

配电系统

电路板设计师面临着一个特殊的任务,那就是为赛灵思器件设计一个配电系统 (PDS) 。大多数其它大型密集型集成电路

(如大型微处理器)都要求带有专用的旁路电容器。因为这些器件仅用于执行特定任务,其电源需求固定而且仅在一定

范围内波动。

赛灵思器件不具有这一属性。器件可以在不确定频率和多个时钟域中执行几乎无限多的应用程序。为此,请您务必参

考器件 《 PCB 设计指南》 [ 参照 37] ,全面了解器件 PDS 。

PDS 设计期间应考虑的关键因素包括:

•

根据功耗估算,来选择合适的电压调节器,满足噪声和电流要求。如需了解更多信息,请参阅 第 5 章中的 “ 功耗分

析与优化 ” 。

提示: 可考虑添加一个分流电阻,便于监控每条供电线上的功耗。

•

整合功耗。如需了解更多信息,请参阅 《 UltraScale 架构 PCB 设计用户指南》 (UG583) [ 参照 37] 中的 链接 。

•

建立 XADC 电源 ( Vrefp 和 Vrefn 引脚)。

•

运行配电网络 (PDN) 仿真。根据特定的器件利用率与步载参数,《 PCB 设计指南》 [ 参照 37] 可以为您的器件提供

去耦电容数量的建议。如果器件利用率与步载参数与您的设计不匹配,建议您运行 PDN 仿真。为确保电源状态处

于所建议的工作范围内,运行 PDN 仿真将有助于确认所需的去耦电容器数量。

如需了解更多有关 PDN 仿真的信息,请参阅赛灵思白皮书:《使用 S 参数模型仿真 FPGA 电源完整性》 (WP411) [ 参照

51] 。

PCB 设计的具体考虑因素

PCB 设计应考虑到与 FPGA 器件进行最快速度的信号连接。这些高速信号在追踪走线结构、过孔、损耗和串扰时非常敏

感。对于多层 PCB ,这几个方面会变得尤为突出。对于高速接口,请进行信号完整性仿真。必要时可以采用更先进的

PCB 材料或改变走线几何图形来重新设计开发板,以获得所需的性能。

赛灵思建议您在设计 PCB 时遵循下列步骤:

1.

查看以下器件文档:

°

对应您器件的 《 PCB 设计指南》 [ 参照 37] 。

°

对应您器件的 《收发器用户指南》 [ 参照 41] 中的电路板设计指导。

2.

查看 IP 产品指南中存储器 IP 和 PCIe ® 的设计指导。

3.

采用 Vivado ® 工具验证您的 I/O 管脚分配:

°

运行同步开关噪声 (SSN) 分析。

°

运行内置的 DRC 。

°

导出 I/O 缓存信息规格 (IBIS) 模型。

4.

以下列方式运行信号完整性分析:

°

针对千兆位收发器 (GT) ,使用信道参数运行 Spice 或 IBIS-AMI 仿真。

°

对于性能更低的接口,运行 IBIS 仿真检查过冲或下冲问题。

5.

使用 Xilinx Power Estimator (XPE) ,并将工艺参数设为 “Maximum” 为设计的功耗生成早期估算。

提示: 您可以通过 set_operating_conditions -design_power_budget <Power in Watts> Tcl 命令使用该

早期估算结果,确保在设计实现阶段完成功耗预算检查。

6.

遵循对应您器件的原理图检查表完成工作。