目录

01 | 引 言

02 | 环境描述

03 | 原理图工具介绍

04 | 原理图设计基本操作

05 | 生成页间引用

06 | 元件自动编号

07 | 结 尾

01 | 引 言

书接上回,在前文中讲述了怎样制作常用的库元件,如电阻、二极管,IC器件,以及怎样放置电子元件;

本篇笔记主要讲述原理图设计过程中的基本操作、页间参考生成,以及元件如何自动编号。

上期参考文章:

《Cadence学习笔记之---库元件制作、元件放置》;

02 | 环境描述

操作系统:Win 11;

软件版本:Allegro Cadence 17.4 (备注:已打补丁);

软件配置:默认设置; (备注:无安装任何插件);

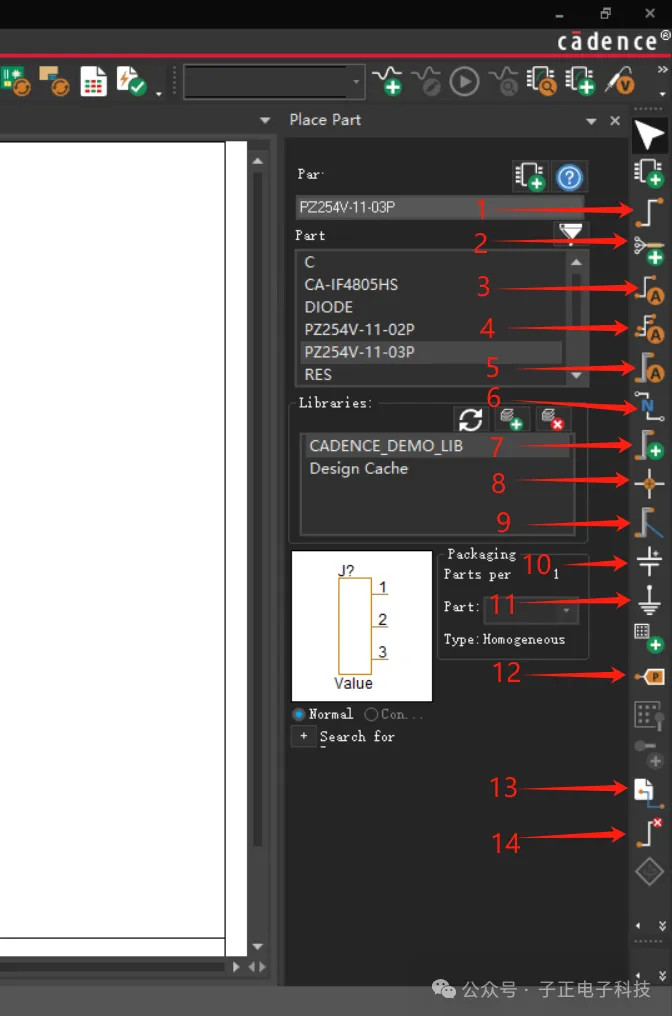

03 | 原理图工具介绍

在设计原理图之前,先介绍一下原理图设计过程中所需要的工具;

这些工具在打开Cadence的 OrCAD Capture 原理图软件后,默认显示在右侧标栏中。

<1>、电气连接;(用于连接各个元件的引脚)

<2>、放置网络组;(在画网络接口的时候很好用)

<3>、自动连接两个电气点;

<4>、自动连接多个电气点;

<5>、自动连接总线;

<6>、放置网络标号;(利用网络标号可将复杂电路拆解为简单电路)

<7>、总线电气连接;(与<1>类似,但用于总线)

<8>、放置电气点,使两条电气线相交;

<9>、放置总线出口;

<10>、放置电源;

<11>、放置参考地;

<12>、放置分层电路入口;(设计层次电路时使用)

<13>、放置跨页连接符;

<14>、设置引脚无连接;(禁用引脚)

在这些工具中,频繁使用的只有<1>、<6>、<10>、<11>、<13>、<14>。

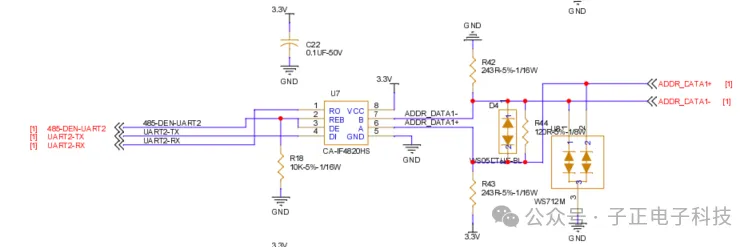

04 | 原理图设计基本操作

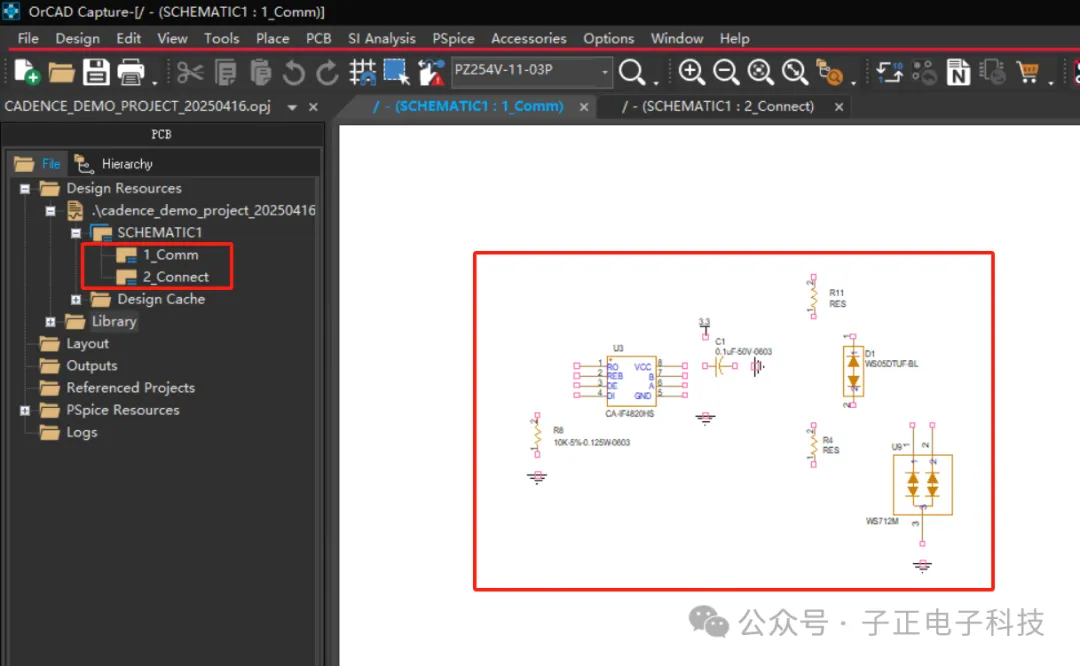

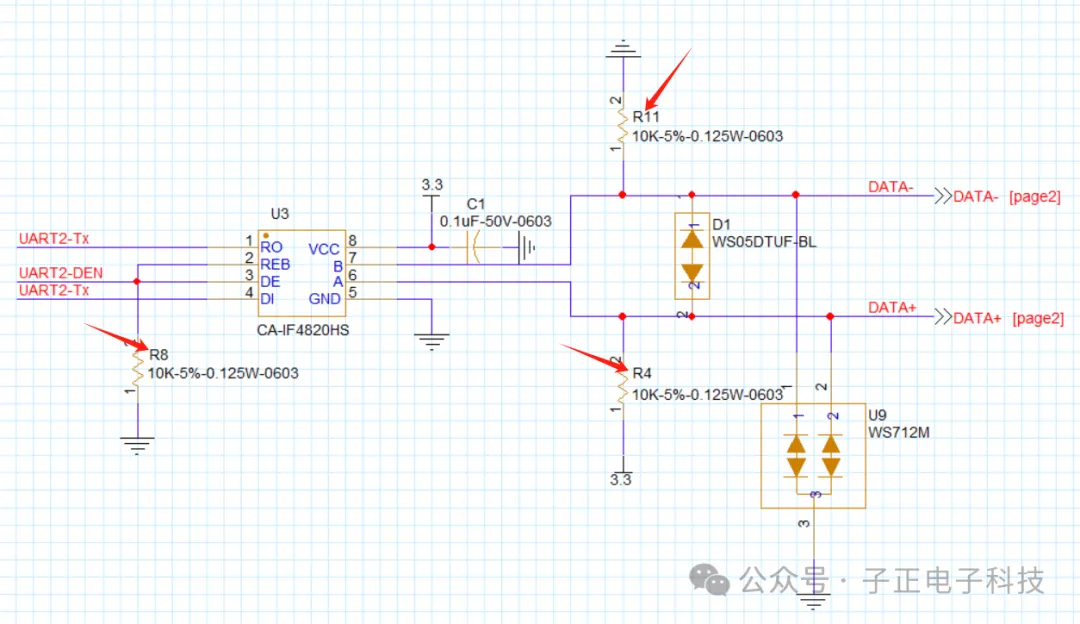

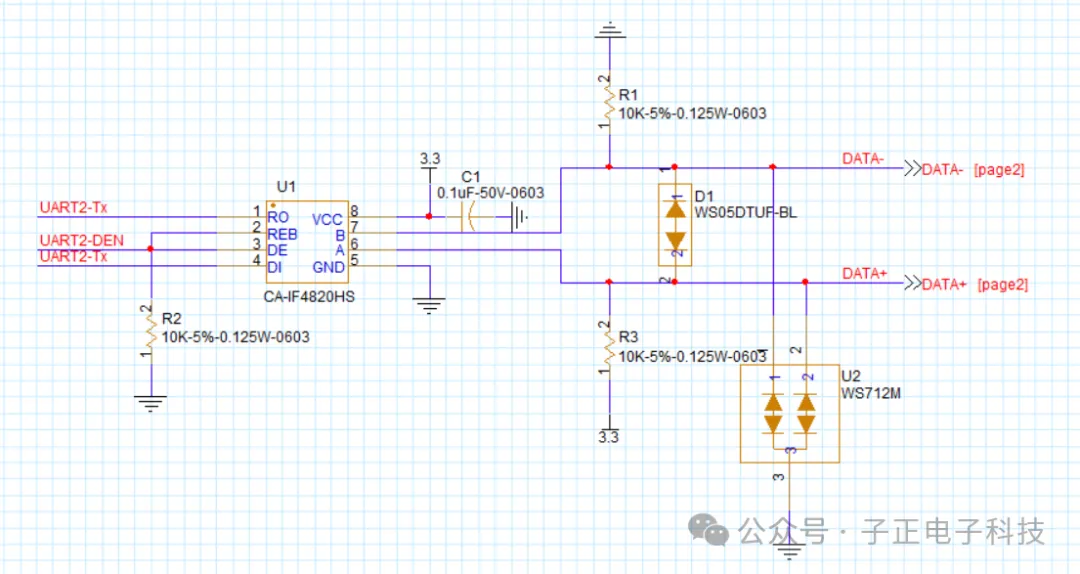

以上面这个RS-485电路为例,我们使用上面介绍的工具进行原理设计;

首先,我们需要按照前面的两篇文章《Cadence学习笔记之---原理图工程、元件库创建》,《Cadence学习笔记之---库元件制作、元件放置》中的操作,新建两个原理图页,并放置需要的电子元件。

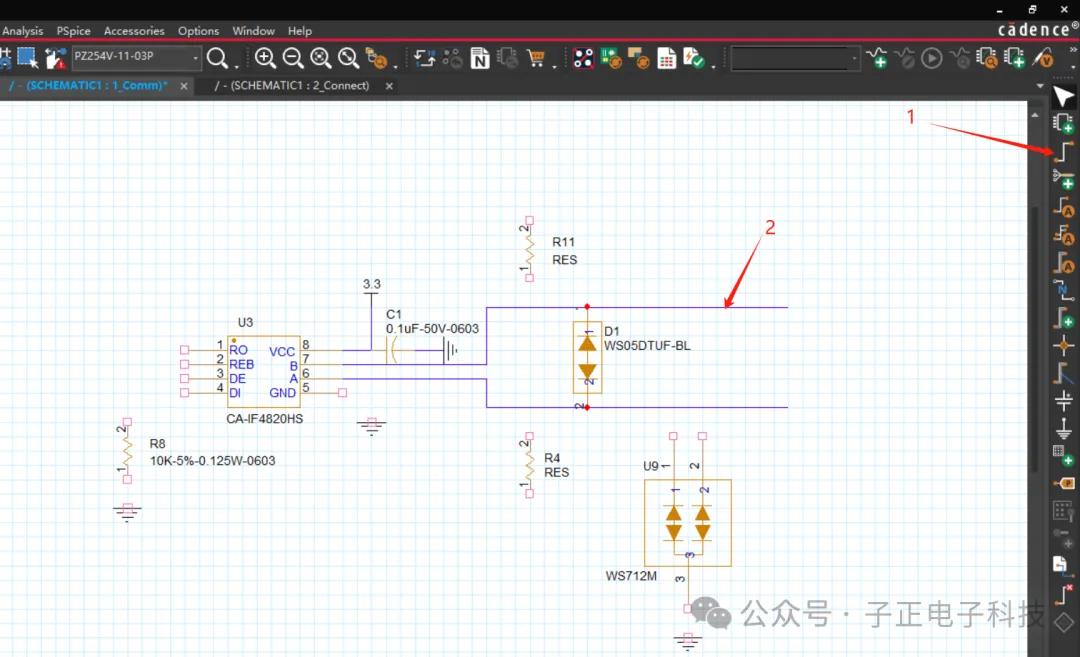

<1>、点击电气连接线;

<2>、点击引脚就可拉出电气线,在结束的位置点击并按下ESC键即退出连接;(电气连接线的快捷键是W键

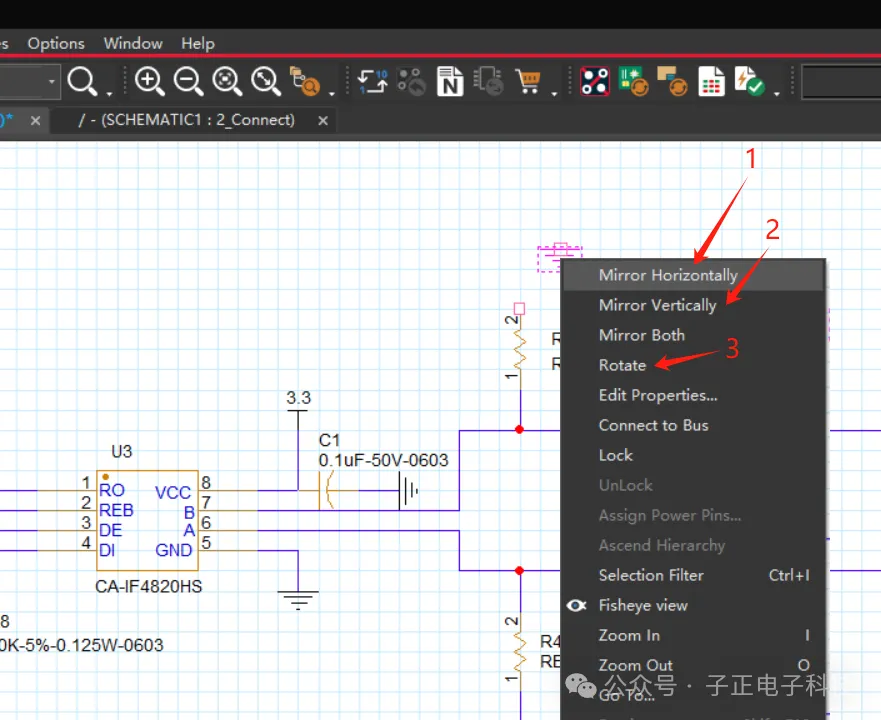

当元件引脚朝向相反时,需要旋转元件以调整位置;

<1>、水平方向对调;

<2>、垂直方向对调;

<3>、按逆时针旋转90°;

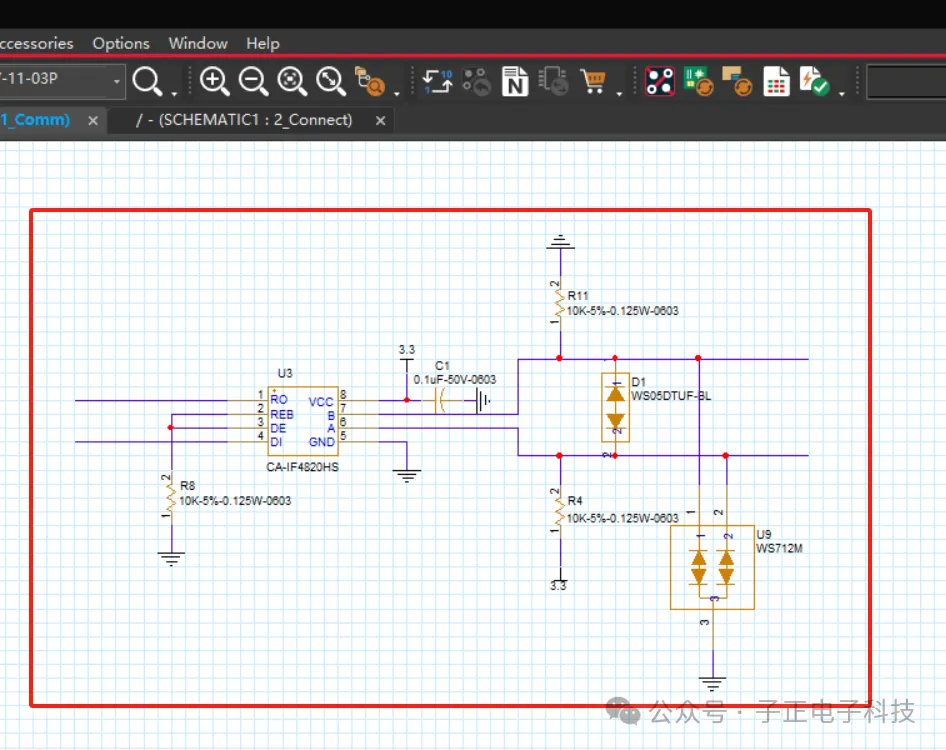

这是连接好所有电气线之后的样子;(注意,在元件摆放的时候要考虑到尽可能的紧凑、直观、协调;最简单的评判方式,如果自己都看不过去,那说明摆放的问题很大)

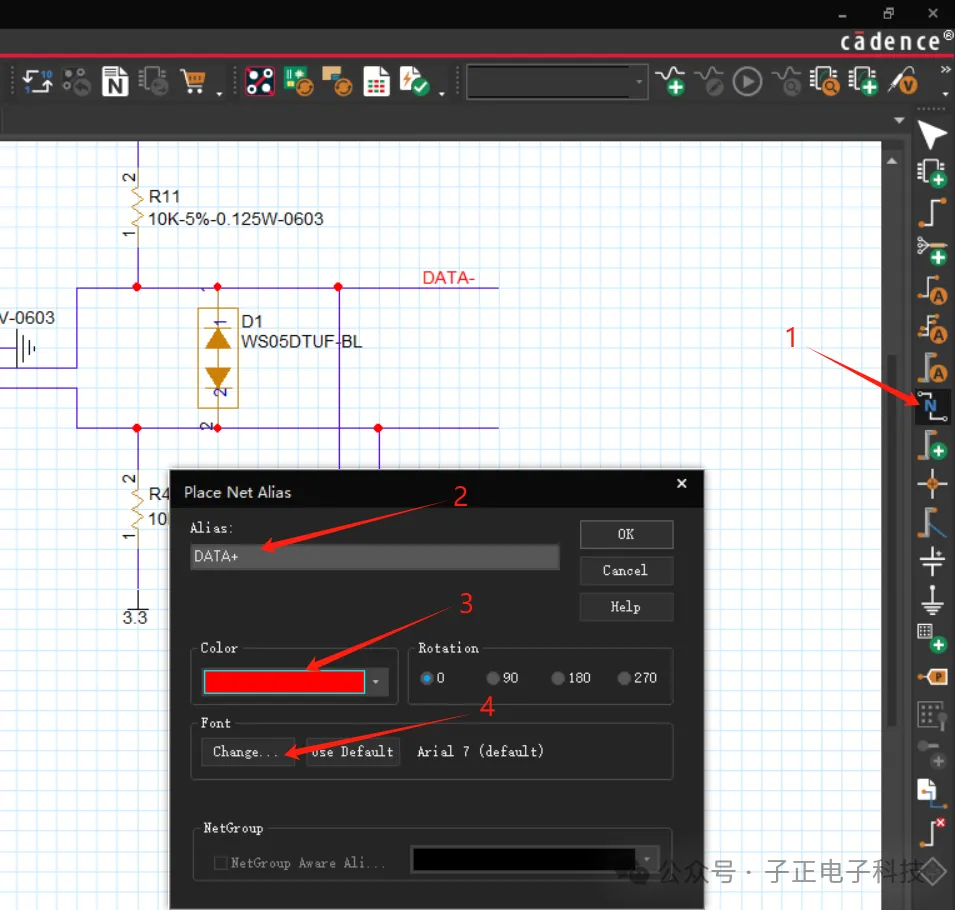

<1>、放置网络标号;

<2>、设置网络标号的名称;

<3>、设置网络标号的颜色;(尽可能选择亮色,易于分辨)

<4>、修改网络标号的字体;(保持默认即可)

放置网络标号的作用是,当同一页原理图中,有别的电路部分需要连接到这个网络时,不需要直接进行电气连接,只需要放置一个同名的网络标号即可;

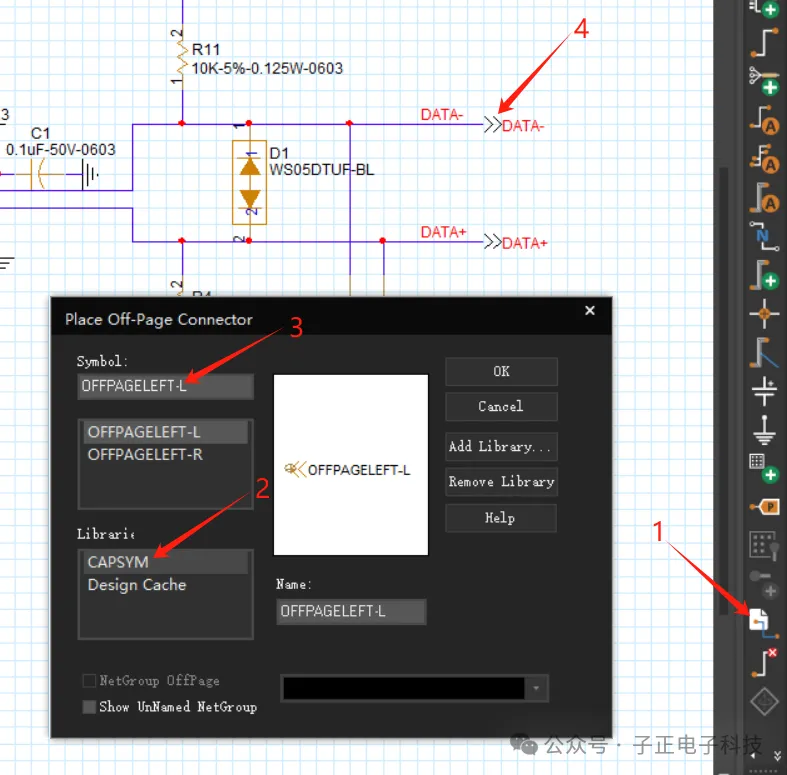

<1>、选择放置跨页连接符;

<2>、选择连接符库;(CAPSYM是系统默认的,也可以自制双向连接符)

<3>、选择向左、或者向右的连接符;

<4>、将连接符放到电气连接点;

跨页连接符原理图设计中必不可少的,很多时候我们需要将原理图拆分成各个模块,单独设计,模块之间常有电气耦合,这个时候就需要用跨页连接符来进行桥接。

原理图设计至此基本就讲述完毕,使用好上面介绍的几个工具,就足以应对日常的工作需要,剩下不常用的工具,可以根据需求再行研究即可。

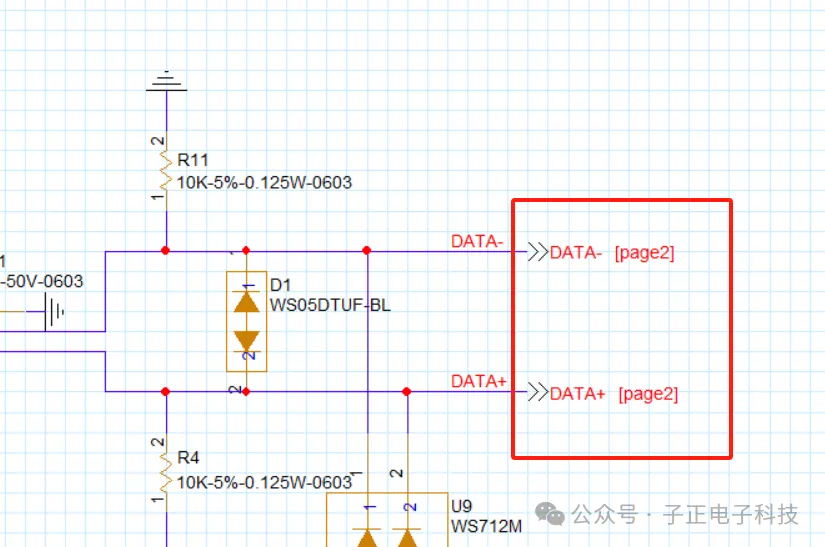

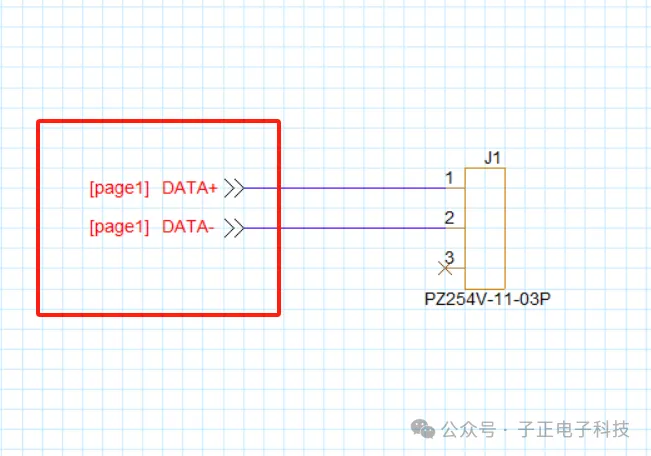

05 | 生成页间引用

如果我们的原理图上只有跨页连接符还不够,因为面对大型电路,原理图页可能有几十页,我们还需要知道这个页连接符还出现在哪一页;

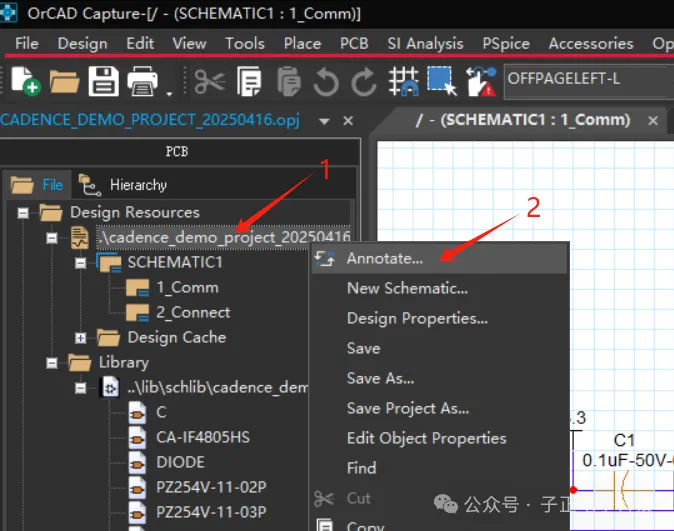

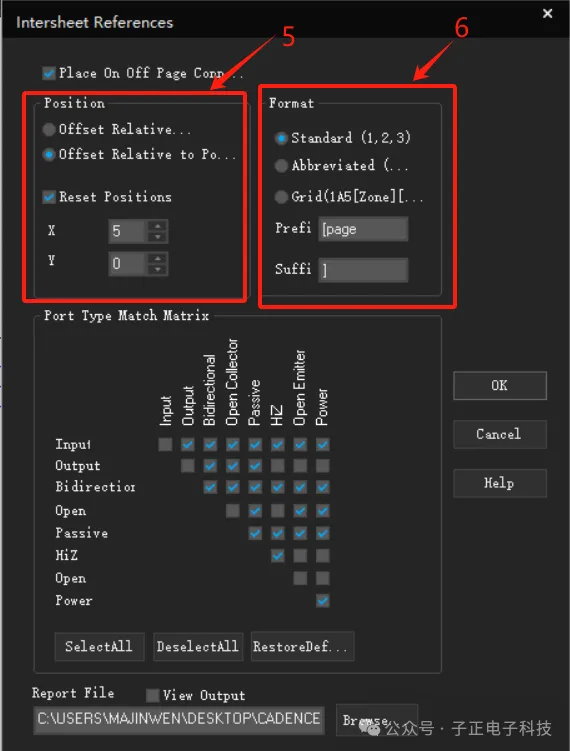

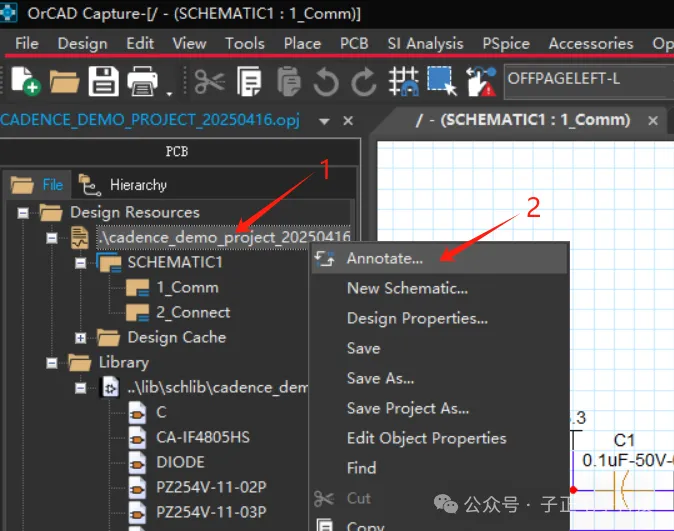

<1>、选择项目管理文件;

<2>、打开 Annotate 设置;

<3>、增加页间参考;

<4>、删除页间参考;(这两项都是批量操作,即增加都增加,删除就全删除)

<5>、设置距离页连接符的偏移量;(一般默认即可)

<6>、设置参考的样式;

以上就是增加页间参考后的最终效果,通过页参考可以很直观的看到电气网络分布的页码,特别需要注意的是,添加页间参考必须保证每个页都有自己的页码号,不能重复。

06 | 元件自动编号

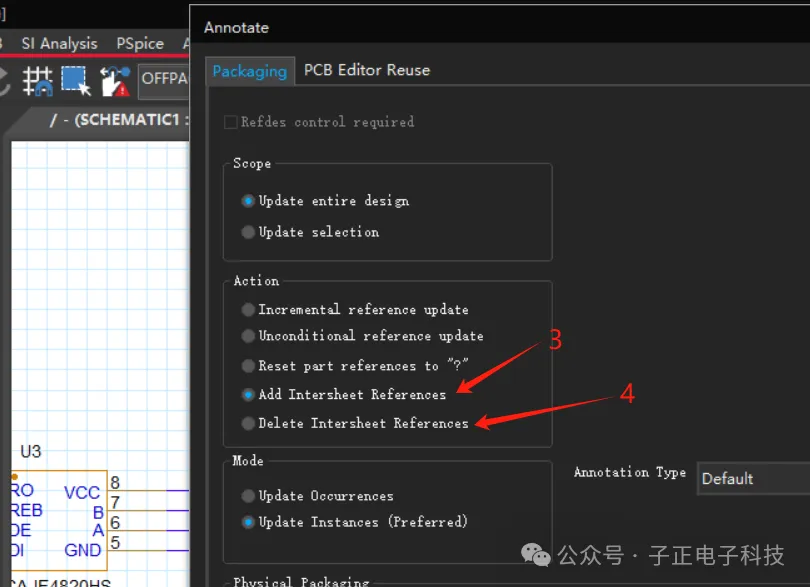

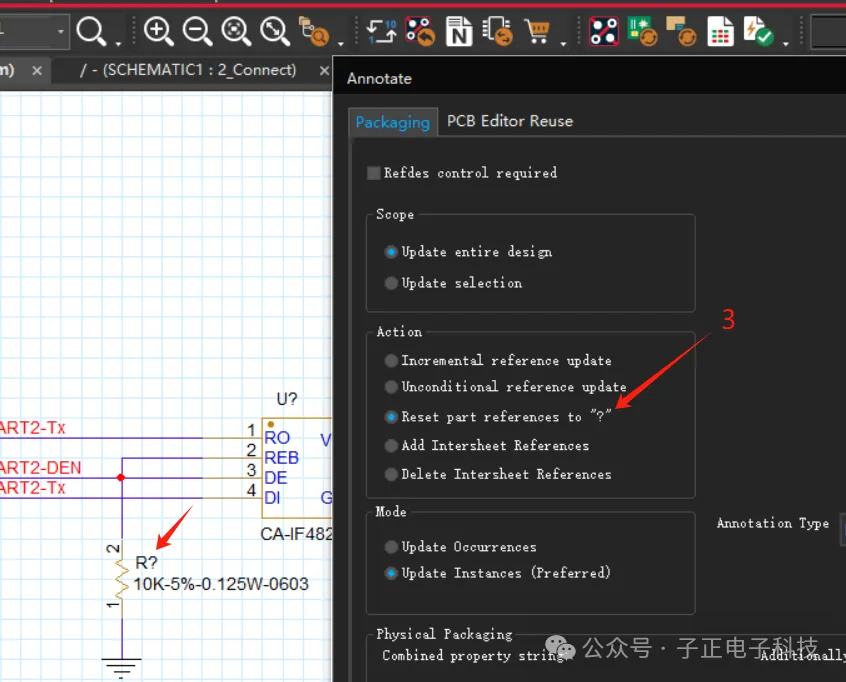

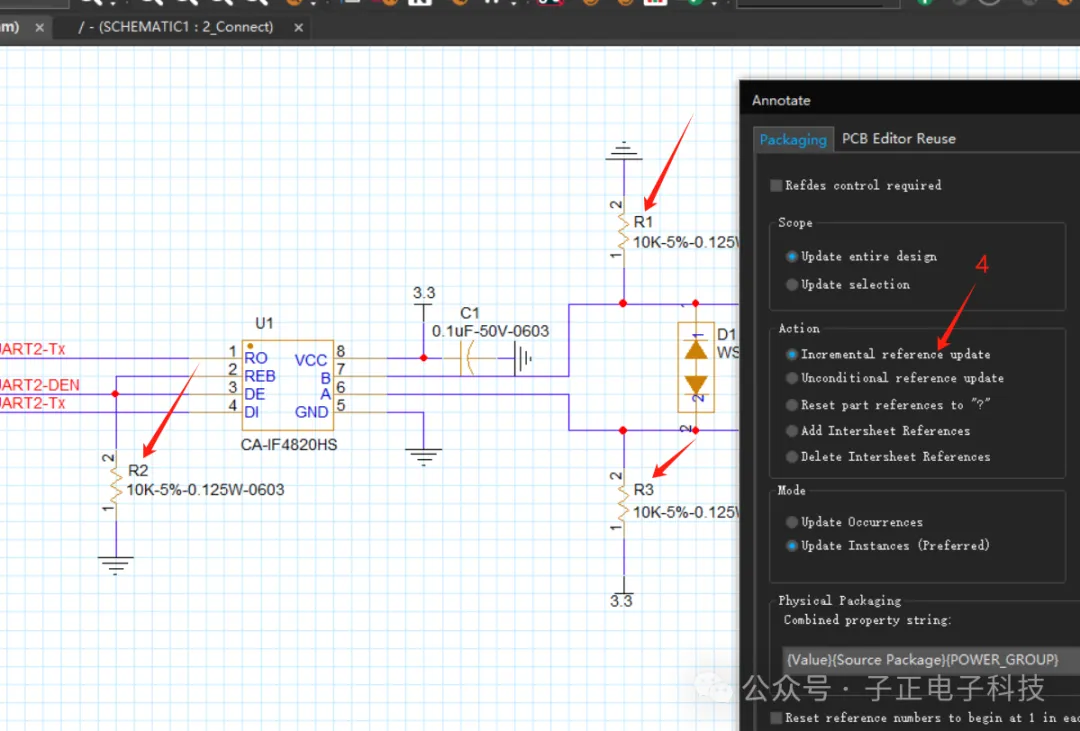

从我们设计的原理图可以发现,经过删删改改,元件的标号很乱,没有顺序,按照我们的预期,同一种元件的序号应该按照顺序排列,这样有利于我们进行后期的BOM管理;

<1>、选择项目管理文件;

<2>、打开 Annotate 设置;

<3>、将元件序号全部重置为无效;

<4>、按照步骤<1>、<2>重新打开设置,设置为按照增量排序;

这里可以看到,最终的效果是元件的序号已经按照我们的设置进行增量顺位排序,起始值为1。

07 | 结 尾

本篇小记只是大致的记录了原理图设计的相关操作,需要强调的是还有很多的细节限于篇幅没有讲到;

但以上这些操作知识,已经可以支撑使用Cadence软件进行常规的硬件设计;在过程中,遇到有疑问的地方,再深入研究,效果会事半功倍。