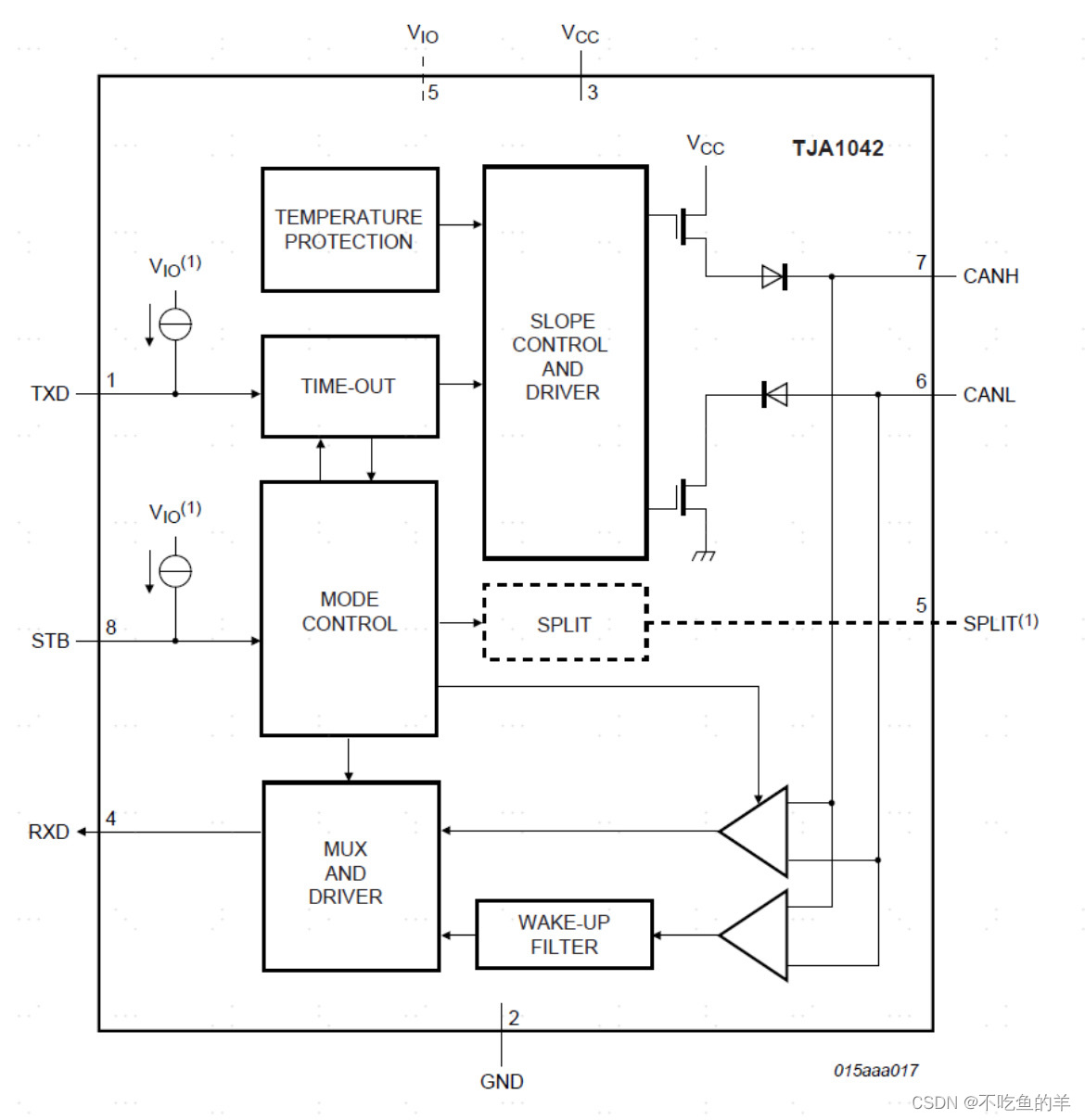

芯片框图

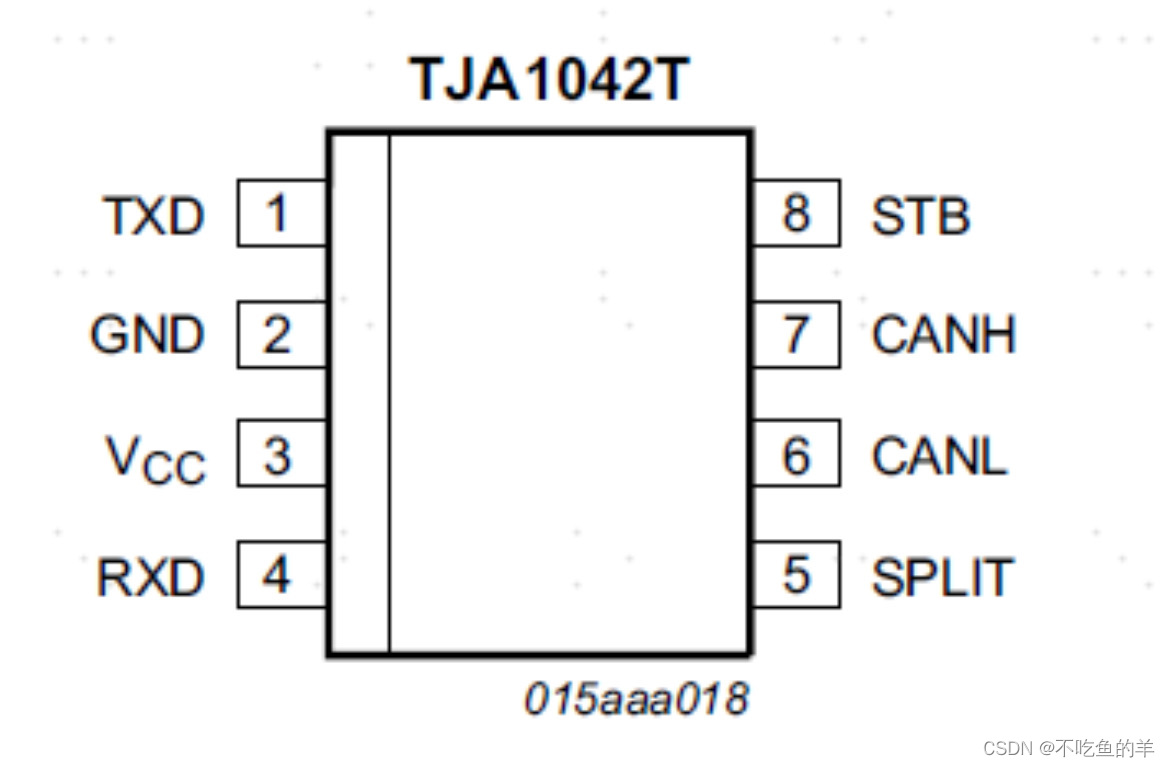

引脚图

引脚功能

| 序号 | 名称 | 功能 |

| 1 | TXD | 主控芯片发送(控制器芯片接收) |

| 2 | GND | 地 |

| 3 | VCC | 电源 |

| 4 | RXD | 主控芯片接收(控制器芯片发送) |

| 5 | SPLIT | 普通模式稳定输出引脚(仅用于TJA1042T) |

| 5 | VIO | 输入引脚适配IO电压(用于TJA1042T/3和TJA1042TK/3) |

| 6 | CANL | CAN低 |

| 7 | CANH | CAN高 |

| 8 | STB | 待机模式控制输入引脚 |

操作模式

| 模式 | STB引脚 | RXD引脚 |

| 普通 | 低电平 | 高电平隐性 低电平显性 |

| 待机 | 高电平 | 高电平不请求唤醒 低电平请求唤醒 |

引脚5的选配

可以配置为SPLIT或者VIO

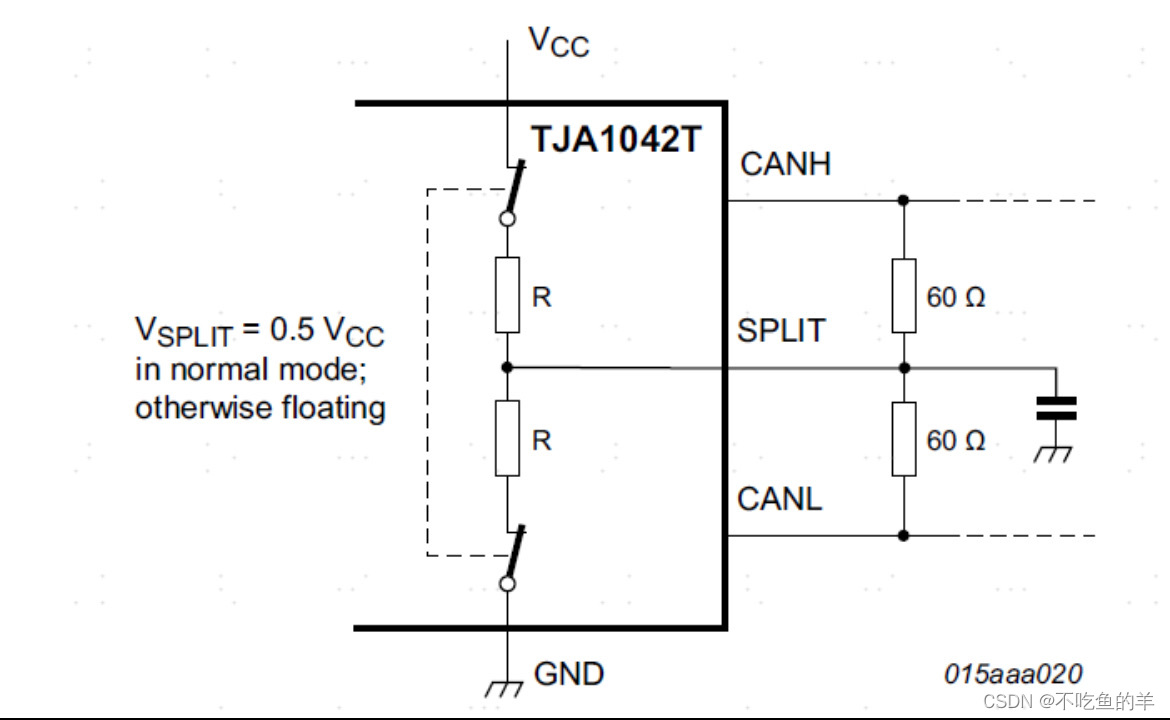

SPLIT引脚

SPLIT引脚可以帮助稳定总线上的隐性电压水平,减少直流漏电到地的网络中的电磁干扰。

在正常模式下,SPLIT引脚提供0.5Vcc的直流输出电压。

在待机模式或Vcc关闭时,引脚SPLIT是浮空的。

不使用时,SPLIT引脚应保持打开状态。

VIO引脚

TTJA1042T/3和TJA1042TK/3上的引脚Vio应连接到微控制器的电源电压。这将调整引脚TXD、RXD和STB的信号电平到微控制器的I/O电平

对于在低功耗模式下运行的应用程序,即使在引脚vcc上没有电源电压,也可以监控总线线路的活动。对于没有Vio引脚的TJA1042版本,Vio输入内部连接到vcc。这将引脚TXD, RXD和STB的信号电平设置为与5 V微控制器兼容的电平。

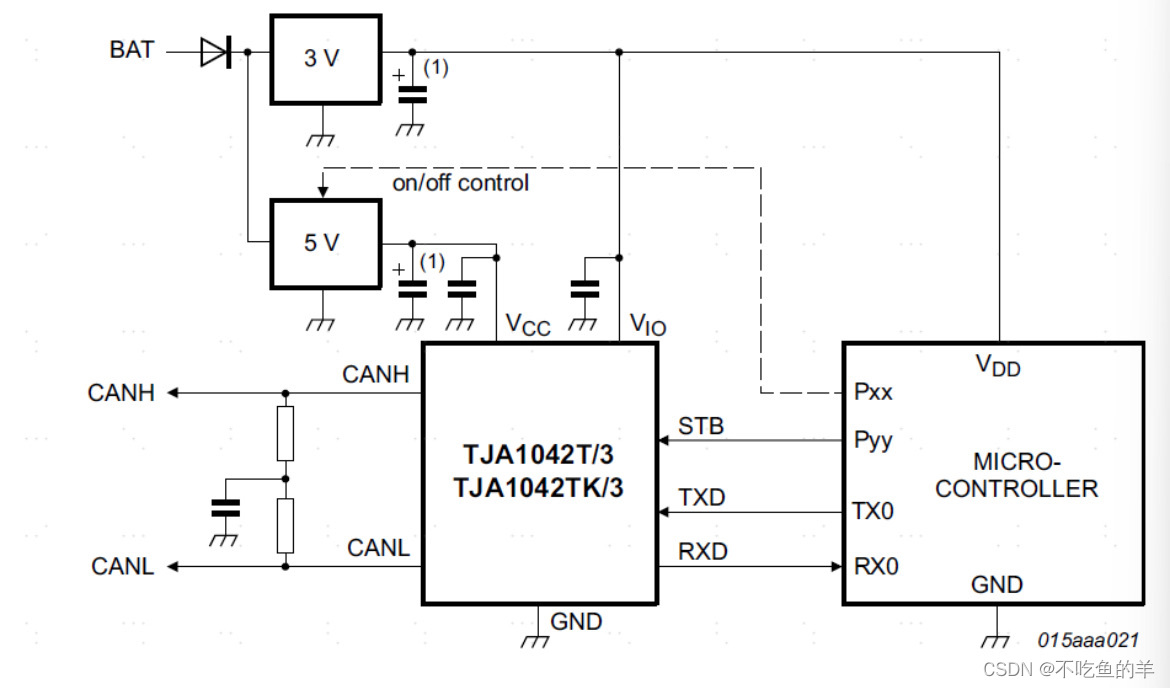

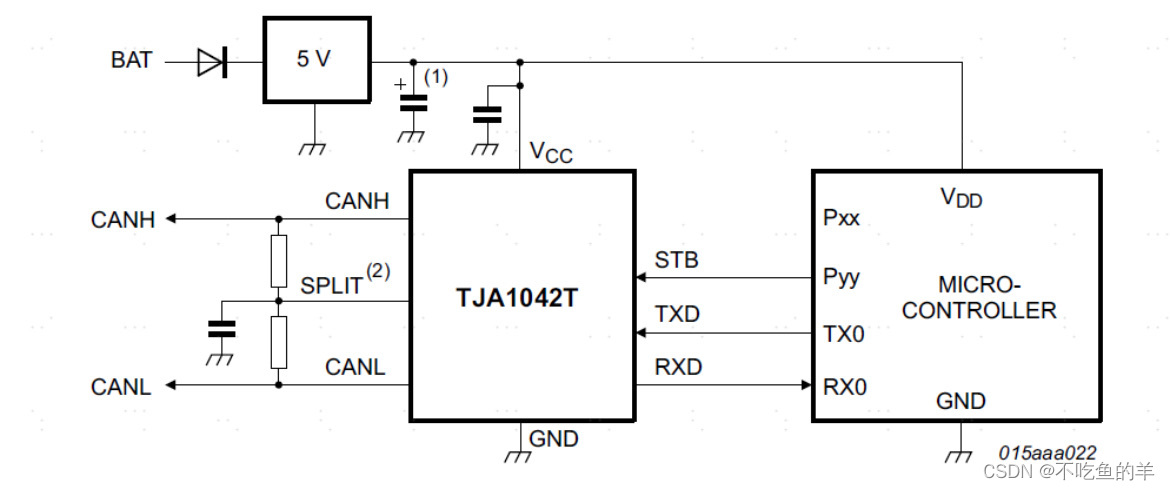

外部原理图

引脚5为SPLIT或者STB

引脚5为STB