IIS协议概述

I²S(Inter-IC Sound)协议,又称 IIS(Inter-IC Sound),是一种专门用于数字音频数据传输的串行总线标准,由飞利浦(Philips)公司提出。该协议通常用于微控制器(MCU)、数字信号处理器(DSP)、数模转换器(DAC)、模数转换器(ADC)、音频编解码器(CODEC)等之间的音频数据交换。

1. I²S 协议基本特征

| 特性 | 描述 |

|---|---|

| 主从结构 | 一般由主设备提供时钟(BCLK 和 LRCK),从设备接收数据或发送数据。通常用于连接一个发送器(Master 或 Transmitter)和一个或多个接收器(Slave 或 Receiver)。 |

| 数据格式 | 串行传输,MSB(最高位)先发送,数据左对齐,通常为 16/24/32 位。 |

| 数据类型 | 一般支持双声道(立体声)数据,左声道和右声道交替传输。 |

| 时钟同步 | 使用两个时钟信号同步数据传输:位时钟(BCLK)和帧时钟(LRCK/WS)。 |

2. I²S 信号线说明

主要的信号线(通常至少 3 条):

- SCK (Serial Clock) / BCLK (Bit Clock): 串行时钟或位时钟。

- 功能: 为总线上的每个数据位提供时钟。每一位数据在 SCK 的一个时钟周期内传输。

- 频率: 通常等于

采样率 (Fs) × 每个通道的位数 (Word Length) × 通道数。例如,对于 44.1 kHz 立体声(2通道)、16位音频,理论上 SCK 至少需要 44.1 kHz * 16 * 2 = 1.4112 MHz。但实际上,为了兼容不同的位深,常常使用固定的 SCK 周期数,例如每个通道帧固定为 32 个 SCK 周期,此时 SCK = Fs * 64 = 44.1 kHz * 64 = 2.8224 MHz。 - 谁驱动: 通常由 Master 设备驱动。

- WS (Word Select) / LRCLK (Left-Right Clock): 字选择或左右声道时钟。

- 功能:

- 指示当前传输的是哪个声道的数据(通常:Low = 左声道,High = 右声道,但也可能相反,需查阅设备手册)。

- 标记每个音频样本(“字”)的开始。

- 频率: 等于音频的采样率 (Fs)。例如,对于 44.1 kHz 音频,WS 信号的频率就是 44.1 kHz。

- 谁驱动: 通常由 Master 设备驱动。

- 功能:

- SD (Serial Data) / DIN / DOUT: 串行数据线。

- 功能: 承载实际的 PCM 音频数据。数据是串行传输的,通常是最高有效位 (MSB) 优先。

- 方向: 从发送器 (Transmitter/Master/Slave) 到接收器 (Receiver/Slave)。可能有 DIN(数据输入)和 DOUT(数据输出)分开的引脚。

可选信号线:

- MCLK (Master Clock):主时钟(有时也叫 SYSCLK)。

- 功能: 提供一个比 SCK 更高频率的系统时钟,通常供 DAC 或 ADC 内部的Σ-Δ调制器等部件使用。

- 频率: 通常是采样率 Fs 的整数倍,如 128Fs, 256Fs, 384Fs, 512Fs 等。

- 谁驱动: 通常由系统中的主时钟源(可能是 Master 设备,也可能是独立的晶振)驱动。并非所有 I²S 实现都需要 MCLK。

| 信号线 | 全称 | 说明 |

|---|---|---|

| BCLK | Bit Clock | 每发送一个比特就跳变一次。数据线 DIN 在 BCLK 上升沿或下降沿有效(取决于实现)。 |

| LRCK/WS | Word Select | 指示当前数据是左声道还是右声道。低电平表示左声道,高电平表示右声道。 |

| DIN | Data Input | 数据线,主机输出音频数据,从设备读取(如 MAX98357)。 |

| DOUT | Data Output | 麦克风(如 INMP441)将音频数据通过此引脚发送出去。 |

| MCLK(可选) | Master Clock | 可选的主时钟,一些系统使用(如 CODEC),但许多模块如 MAX98357 不需要。 |

3. 工作模式

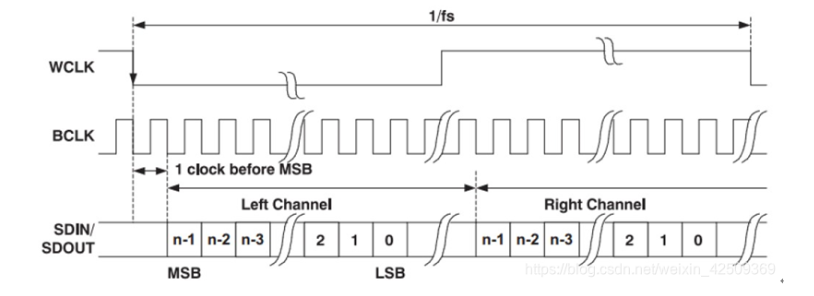

Standard I²S (飞利浦标准): 数据在 WS 变化后的第二个 SCK 周期开始传输。左右通道的数据MSB均是在WS变化后第二个SCK/BCLK上升沿有效。

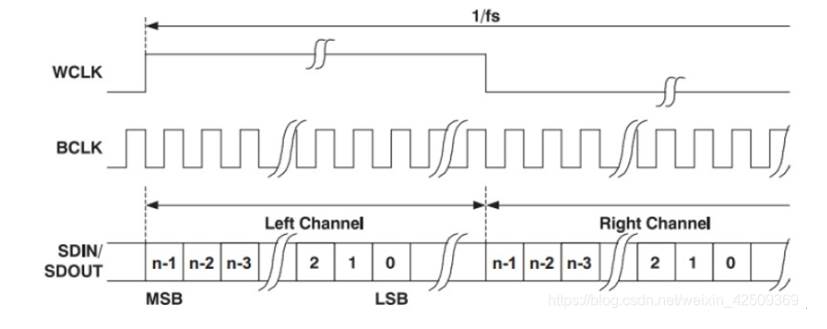

Left-Justified (左对齐): 数据在 WS 信号变化的同时(或第一个 SCK 周期)就开始传输 MSB。具体如下图所示:

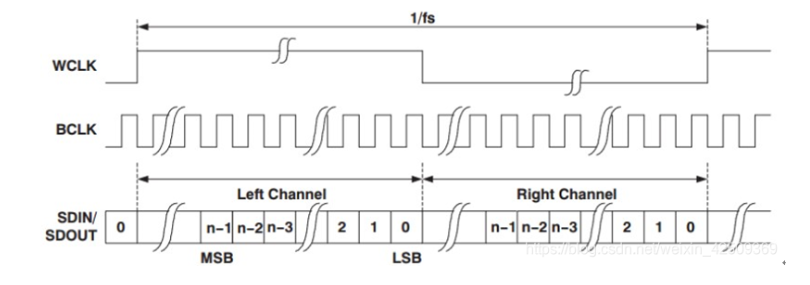

Right-Justified (右对齐): 数据的 LSB 紧靠在 WS 信号下一次变化之前的最后一个 SCK 周期对齐。

- 接收设备必须事先知道待传数据的字长。

- 左右对齐模式的WS时钟高电平为左声道,低电平为右声道,刚好与标准IIS相反。

- SCK = 采样率(48K、44.1K、16K等) x 字长(16bit、24bit、32bit) x 2(左右两通道)

图片参考来自:IIS接口详细介绍-CSDN博客